文章來源:半導體行業觀察。

隨著摩爾定律逐步進入平臺期,目前半導體芯片的性能提升已經越來越多地依賴芯片架構設計以及高級封裝技術的提升,而不是依靠半導體工藝體征尺寸的下降。另一方面,隨著人工智能時代的來臨,越來越多的計算芯片設計需要考慮人工智能對于算力的需求。因此,如何在未來十年內為人工智能應用來設計和優化相關的芯片架構、工藝以及封裝系統就成了學術界和工業界都非常關注的問題。

在上周召開的2021國際電子器件大會(IEDM 2021)中,我們就看到了許多相關的研究發表,而其中非常值得我們關注的就是一篇來自MIT和斯坦福大學的論文,標題為《The Future of Hardware Technologies for Computing: N3XT 3D MOSAIC, Illusion Scaleup, Co-Design》(《面向計算的未來硬件平臺:N3XT 3D MOSAIC與Illusion Scaleup協同設計》)。該研究并非是一日之功,而是以MIT和斯坦福大學為代表的美國半導體工藝學術研究學派在超高密度3D集成領域多年研究的最新成果,并且還規劃了未來的路線圖。

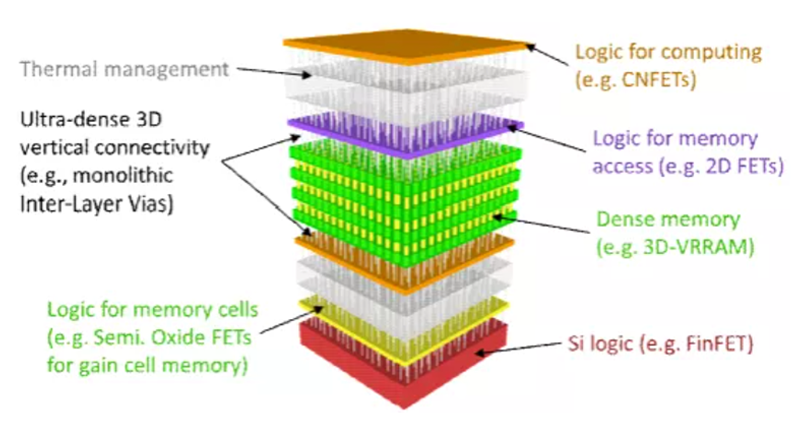

目前,雖然以TSV為代表的3D集成技術已經成熟,但是3D集成的通孔之間的間距仍然較大,在10um數量級。為了能進一步提升3D集成密度,美國半導體學術界(以斯坦福的黃漢森,Subhasish Mitra和MIT的Max Shulaker為代表)提出的方案是使用碳納米管技術。碳納米管技術的一個重要優勢就是可以實現超高密度3D堆疊通孔,其通孔間距可縮小至100 nm,比目前的TSV通孔間距縮小了兩個數量級。同時,考慮目前人工智能應用,其主要的性能瓶頸在于內存訪問,因為人工智能所需要的神經網絡模型運行時無論是權重還是中間結果都需要大量的內存資源,因此需要把存儲器和計算邏輯以非常高的效率集成在一起。兩者相結合,就是使用碳納米管技術和超高密度3D集成技術把計算和(新)存儲器集成在一起,而美國半導體學界提出的解決方案就是N3XT,全稱是“基于納米工程的計算系統技術”。具體來說,N3XT把多種使用不同工藝實現的芯片層(包括用傳統硅工藝實現的數字邏輯,使用下一代存儲器工藝實現的高密度存儲器,使用碳納米管工藝實現的計算邏輯等)使用超高密度3D集成通孔集成到了一起。

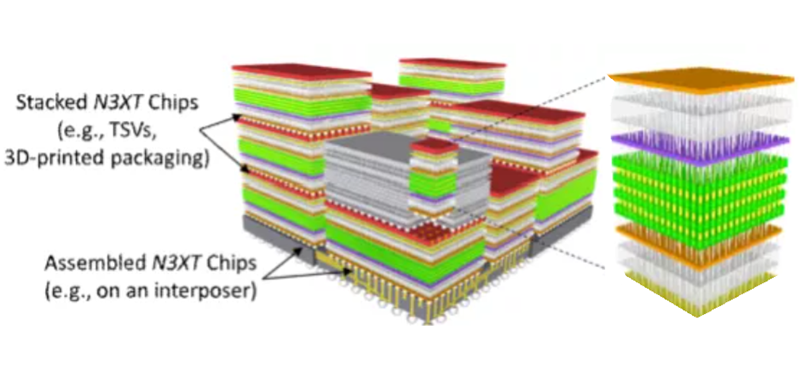

以N3XT為單元,還可以把多個不同的N3XT單元(以及傳統的芯片)以各種形式進一步集成到一起,例如可以用TSV的形式把多個N3XT單元堆疊在一起,也可以用2.5D封裝的形式把多個N3XT封裝到通過一個硅基板上,由此實現超大規模的異構集成。這種把多種芯片以各種方式集成到一起的方案稱之為MOSAIC(即Monolithc/stacked/assembled IC,指以各種不同形式集成到一起的芯片單元)。

至此,該研究中的主要工藝和器件技術(即論文標題中的N3XT 3D MOSAIC)已經呈現在了我們眼前。下一步就是如何在系統層面上最大化這種規模化集成的效率。

超高密度3D集成配合系統優化實現千倍性能提升

隨著人工智能對算力的需求越來越高,未來的N3XT系統也需要考慮在系統層面上如何最優化以滿足人工智能的算力需求;換句話說,如果給100個N3XT系統,如何最優化地分配任務,讓整體計算效率最高?這個問題如果能解決地好,就能很好地處理N3XT系統對于人工智能計算問題的規模化(scale-up)。

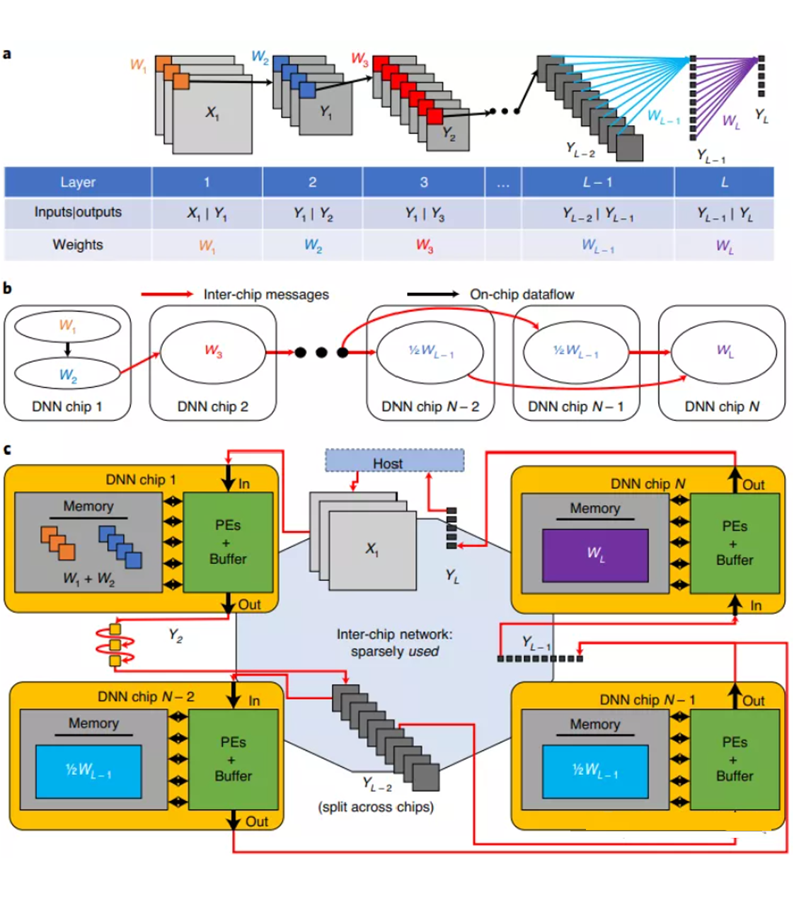

對此,研究者提出的方案是Illusion Scaleup。Illusion scaleup主要是針對人工智能應用中的深度學習算法。該系統設計方法中,首先把整個神經網絡分割成多個部分,并且給每個N3XT模塊分配一部分計算任務。例如,分割可以以神經網絡層為單位,當一層的計算量比較小的時候,可以在單個N3XT模塊上分配多個層的計算;當一層的計算量較大時,則可以把一層網絡也分割成多個部分給不同的N3XT模塊。由于神經網絡不同的層之間是串行計算關系,因此通過這種以層為單位來分割工作量,就可以讓不同的N3XT模塊之間以流水線的方式工作。另外,由于每個N3XT只負責一層計算,因此可以確保神經網絡的權重不用在模塊間移動,而僅僅只需要移動中間結果,這樣就大大減小了數據移動帶來的額外開銷。

最后,由于N3XT系統可以使用下一代非易失性存儲器,例如RRAM,因此可以支持快速開關,針對于此作者還提出了可以利用此特性在不需要使用某個N3XT單元的時候把它關閉,從而可以大大節省漏電流。使用這樣的策略,可以通過線性增加每個N3XT的性能(例如增加N3XT堆疊層數,以及N3XT之間的互聯帶寬)來滿足人工智能計算對于算力指數級上升的算力。使用這樣的方法,研究表明整個N3XT 3D MOSAIC可以實現比目前3D堆疊100-1000倍的性能提升。

超高密度3D集成商用化的道路

目前美國半導體學術界對于碳納米管和N3XT相關技術的商用化決心很大,目前也有不錯的成果。整體來說,碳納米管在美國的商業化過程中包括了多方的加入:美國政府研究機構DARPA,高校MIT和斯坦福,以及美國專門負責先進半導體技術代工的代工廠SkyWater。DARPA從多年前就開始大力資助碳納米管相關的下一代半導體工藝研究,兩年前,MIT的Max Shulake已經帶領研究組在SkyWater實現了首個碳納米管和RRAM的3D堆疊芯片晶圓,而在最近的兩年中,同樣的團隊陸續完成了多個里程碑,包括首個碳納米管實現的超大規模集成電路(RISC-V處理器),首個碳納米管PDK等等。同時,在整個碳納米管研究團隊中起領袖作用的斯坦福大學教授黃漢森本人曾于2018-2020年學術休假期間全職擔任TSMC的副總裁,而在回到斯坦福大學之后仍然擔任TSMC的首席科學家職位,相信他也會成為碳納米管超高密度3D堆疊技術商用化的重要橋梁人物。

而在另一方面,在半導體工業界,對于大規模高密度3D封裝的追求也是歷歷可見。例如,AMD今年早些時候發布的3D V-Cache使用了TSMC的最新SoIC技術,可以將3D堆疊通孔間距下降到1um數量級,從而大大增加了3D堆疊的互聯密度。Intel也同樣在今年發布了Ponte Vecchio,可謂是它最雄心勃勃的芯片計劃,借助TSV以及Intel特有的EMIB技術實現了超大規模2.5D和3D互聯以及封裝。半導體業界對于下一代超高密度封裝和互聯非常強的訴求以滿足人工智能高性能計算的需求,在這樣的情況下,我們認為N3XT 3D MOSAIC從學術界的角度給出了一個未來相關技術的進化路線圖,其中至少有一部分(例如3D MOSAIC)會在未來幾年內落地到商用中,而碳納米管技術隨著更多研究和驗證,也可望在稍遠的時間節點正式進入商用。

在中國,相關的碳納米管技術在學術界也有很好的研究積累,北大的彭練矛院士等團隊也在全球頂級期刊上發表了非常具有影響力的研究結果。超大規模高密度3D集成是一項系統工程,需要半導體工藝和器件,先進封裝技術以及電路架構領域的協同發展,我們希望中國的相關技術能從目前的碳納米管器件的單點突破真正拓展到系統級突破,同時配合半導體代工和封裝業界的發展,這樣才能在下一代基于新一代器件和封裝技術的半導體新范式來臨時,能有足夠多的技術積累來引領整個技術潮流的發展。

相關新聞

3D集成新方案,實現千倍芯片性能提升

2021-12-21

隨著摩爾定律逐步進入平臺期,目前半導體芯片的性能提升已經越來越多地依賴芯片架構設計以及高級封裝技術的提升…

索尼全球首發,雙層堆疊CMOS圖像傳感器

2021-12-18

索尼的半導體部門宣布,他們成功開發了世界上第一個具有兩層晶體管像素的堆疊式 CMOS 圖像傳感器技術......

辰卓科技ALS攝像頭模組測試系統助力模組廠良率效率雙提升

2018-02-22

辰卓人就是這么堅定不移地走自主技術創新之路,在未來,辰卓人將在C-PHY,三攝像頭模組測試系統繼續推行ARM Linux System,逐步建立ARM Linux System生態鏈,更嘗試推出成套解決方案:CZTEK Test System,讓模組測試更簡單、更高效。